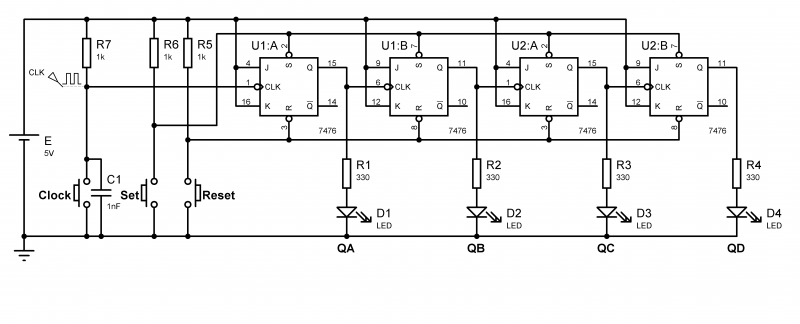

Görsel 6.xx deki asenkron yukarı sayıcı devresi arka arkaya bağlanmış 4 adet JK flip floptan oluşmaktadır. Flip flopların J ve K girişleri kaynağın artı ucuna bağlandığından toggle modunda çalışırlar. Uygulanan her clock palsinde çıkış bir öncekinin tersi olur. Devrede clock palsi sadece ilk flip floba (U1:A) uygulanır. Diğer flip flopların clock girişleri, bir önceki flip flobun çıkışına bağlıdır. Bir önceki flip flobun durum değiştirmesiyle clock palsi alırlar.

Clock palsinin uygulandığı ilk flip flobun çıkışı (QA) en düşük bit değerine sahiptir. Clock palsi Clock butonu ile uygulanabileceği gibi harici bir kaynaktan da clock palsi uygulanabilir. Set butonuna basıldığında tüm flip floplar set edileceğinden çıkışlarına bağlı olan LED’ler yanar. Reset butonuna basıldığında ise flip floplar reset olacağından tüm LED’ler söner.

Görsel 6.xx: : Asenkron yukarı sayıcı devresi

MALZEME LİSTESİ

| Adı | Özelliği | Sembolü | Görünüşü | Miktarı |

| 7476 | IC (Entegre) (DIL-16 kılıf) | 2 adet | ||

| Direnç | 330Ω | 4 adet | ||

| Direnç | 1kΩ | 3 adet | ||

| Kondansatör | 1nF | 1 adet | ||

| LED | Kırmızı | 4 adet | ||

| Buton | Push buton (NO) | 3 adet |

İŞLEM BASAMAKLARI

- Görsel 6.xx’deki devreyi kurunuz.

- Besleme kaynağının (+) ucunu 7476 entegresinin 5 numaralı ayağına, (-) ucunu ise 13 numaralı ayağına bağlayınız. Devreye enerji veriniz.

- Clock butonuna her basıldığından Q çıkış ifadesinin (LED’lerin) durumlarını ve onluk karşılığını Tablo xx’e yazınız.

DEĞERLENDİRMELER

Tablo xx Asenkron Yukarı Sayıcı Devresi

| CLK | Çıkışlar | Decimal eşdeğeri | |||

| QD (D4) | QC (D3) | QB (D2) | QA (D1) | ||

| 0 | |||||

| 1 | |||||

| 2 | |||||

| 3 | |||||

| 4 | |||||

| 5 | |||||

| 6 | |||||

| 7 | |||||

| 8 | |||||

| 9 | |||||

| 10 | |||||

| 11 | |||||

| 12 | |||||

| 13 | |||||

| 14 | |||||

| 15 |

SORULAR

- Asenkron sayıcıların özelliklerini araştırınız.

- Clock palsinin uygulandığı flip flopun bit derecesi nedir?

- Sayma işleminin aşağı doğru olması için devrede nasıl bir düzenleme yapılmalıdır?

Asenkron Sayıcıların Özellikleri:

Asenkron sayıcılar, her bir flip flop’un tetikleme sinyalinin (clock) başka bir flip flop’un çıkışıyla tetiklenmediği sayıcı tipleridir. Özellikleri şunlardır:

- Bağlantı ve Tetikleme: Asenkron sayıcılar, her bir flip flop’un girişlerini, bir önceki flip flop’un çıkışıyla değil, genellikle dış bir tetikleme sinyali ile tetiklerler.

- Gecikme ve Sorunlar: Asenkron sayıcılar, belirli koşullarda gecikme ve yarış durumlarına neden olabilir. Bu durumlar, doğru çalışmayı engelleyebilir veya yanlış sonuçlar üretebilir.

- Daha Az Kullanılır: Günümüzde genellikle senkron (synchronous) sayıcılar daha fazla tercih edilir, çünkü daha az hata eğilimlidirler ve daha düzenli çalışırlar.

Clock Palsinin Uygulandığı Flip Flop’un Bit Derecesi Nedir?

Clock palsi (clock pulse) genellikle flip flop’un herhangi bir bit derecesini belirlemez. Flip flop’un bit derecesi, genellikle veri genişliğine (veri boyutuna) bağlıdır. Örneğin, bir 8-bit flip flop 8 bit veri depolayabilirken, 4-bit bir flip flop sadece 4 bit veri depolayabilir.

Sayma İşleminin Aşağı Doğru Olması İçin Devrede Nasıl Bir Düzenleme Yapılmalıdır?

Sayma işleminin aşağı doğru (down-counter) olması için bir asenkron sayıcıyı veya senkron bir sayıcıyı tersine çevirmek yeterlidir. Bu, mevcut sayma işlemi sırasında herhangi bir giriş darbesi olmaksızın, önceki sayma işleminden daha düşük bir değere doğru gerçekleşir. Bunu gerçekleştirmek için giriş sinyali veya bir kontrol sinyali kullanılarak flip flopların tersine çevrilmesi veya geri sayım işlemine başlanacak değerlerin belirlenmesi gerekebilir.

No responses yet